## Hierarchical Graph Reduction Approach to Symbolic Circuit Analysis with Data Sharing and Cancellation-Free Properties

Yang Song and Guoyong Shi

School of Microelectronics

Shanghai Jiao Tong University

Shanghai, China

#### Content

- Principle of Symbolic Circuit Analysis

- BDD-based Symbolic Stamp Construction

- New Graph-based Hierarchical Method

- Algorithm

- Implementation

- Experimental Results

- Summary

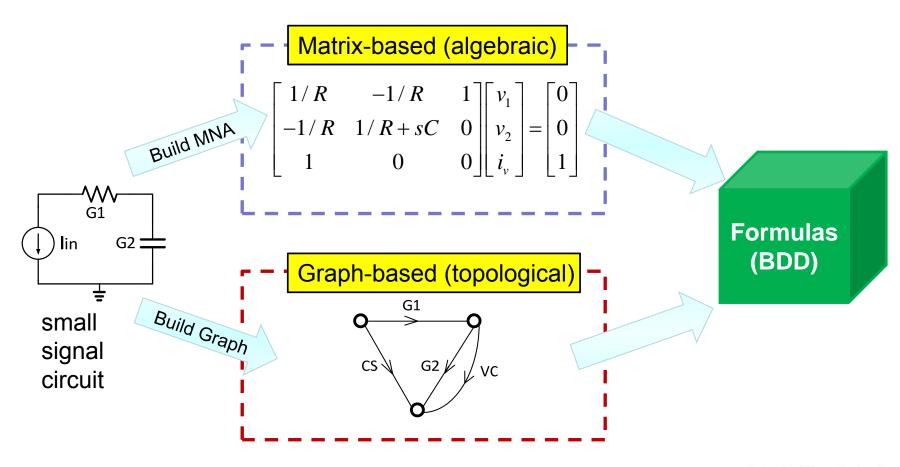

#### Symbolic Methods

From circuit to analytical formulas

#### **BDD-based Methods**

#### Motivation for Hierarchical Analysis

When a circuit block is too large for flat symbolic analysis, we have to partition it and do hierarchical analysis.

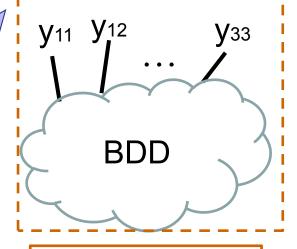

#### **Symbolic Stamp** Construction

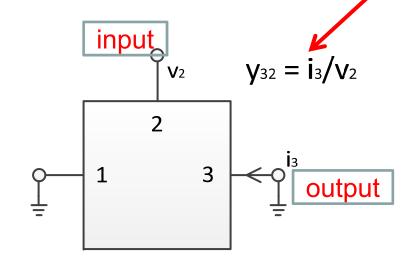

Trans-admittance Matrix / Y Matrix

Symbolic Stamp

Multi-root DDD/GPDD

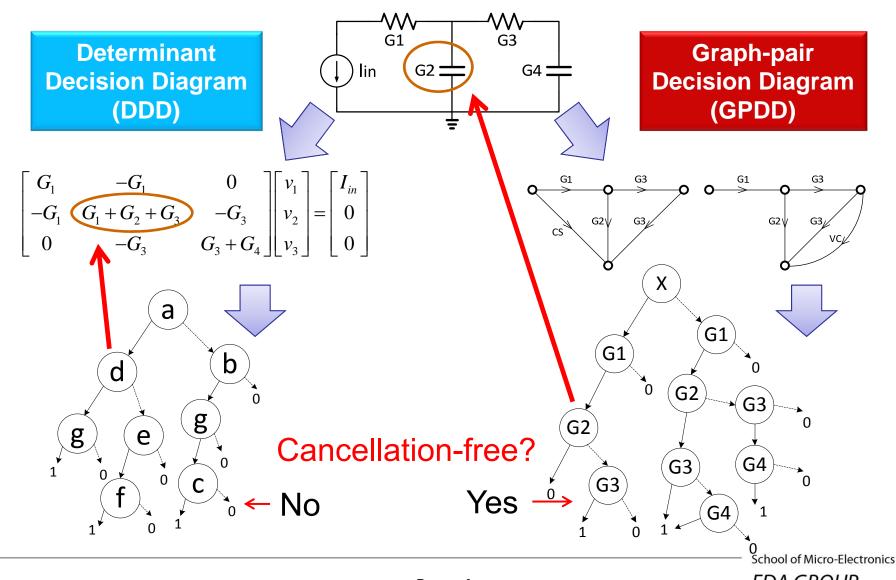

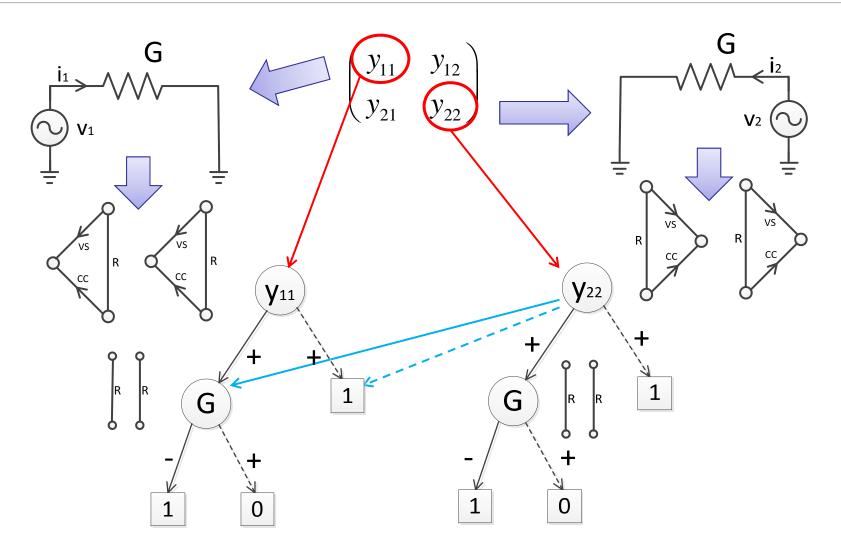

#### Symbolic Stamp by DDD

#### Symbolic Stamp by GPDD

#### Hierarchical Analysis

- Break a large circuit into a nested hierarchy.

- Each module is described by a symbolic stamp.

- Assemble the symbolic stamps in analysis.

Page 9

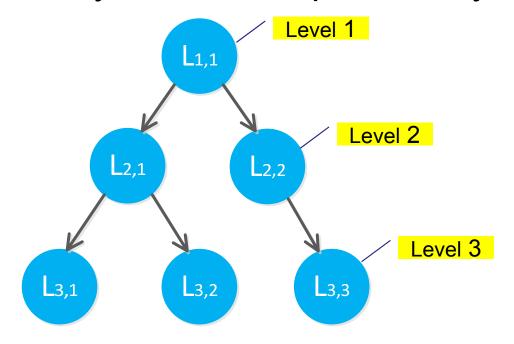

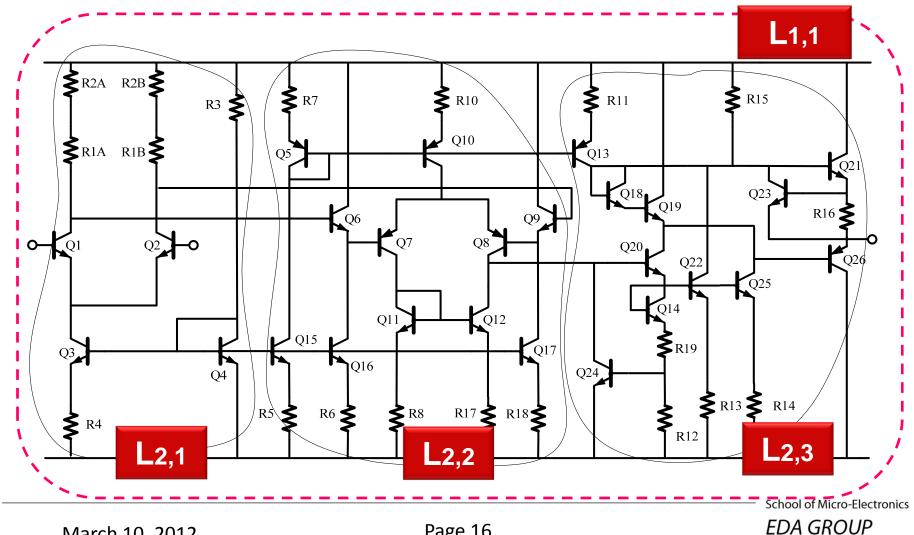

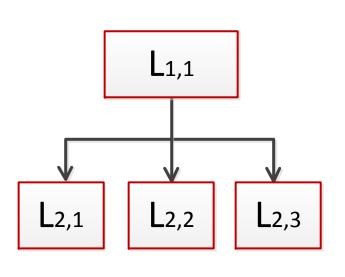

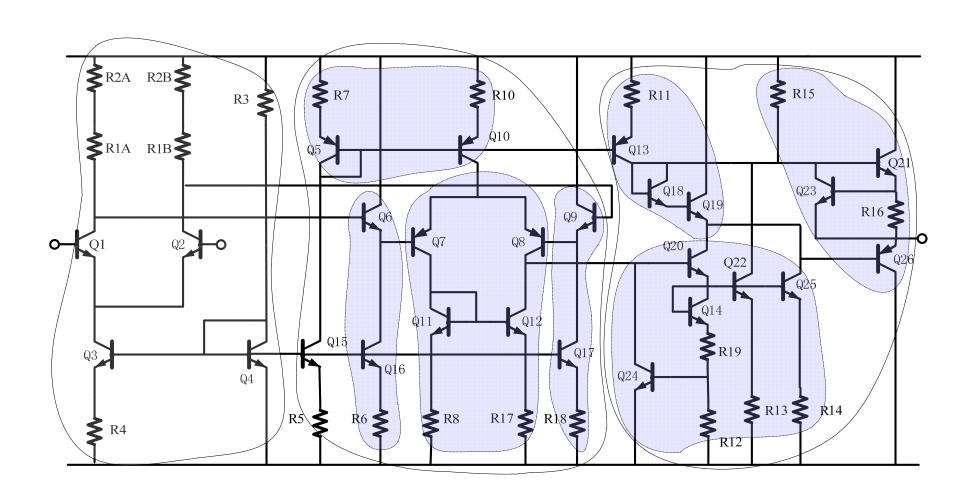

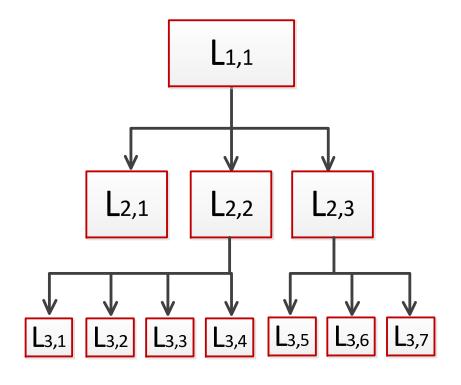

Each Lm,n is a symbolic stamp.

School of Micro-Electronics

EDA GROUP

#### **Hierarchical Constructions**

- Many ways of assembling symbolic stamps

- Typically we consider three methods:

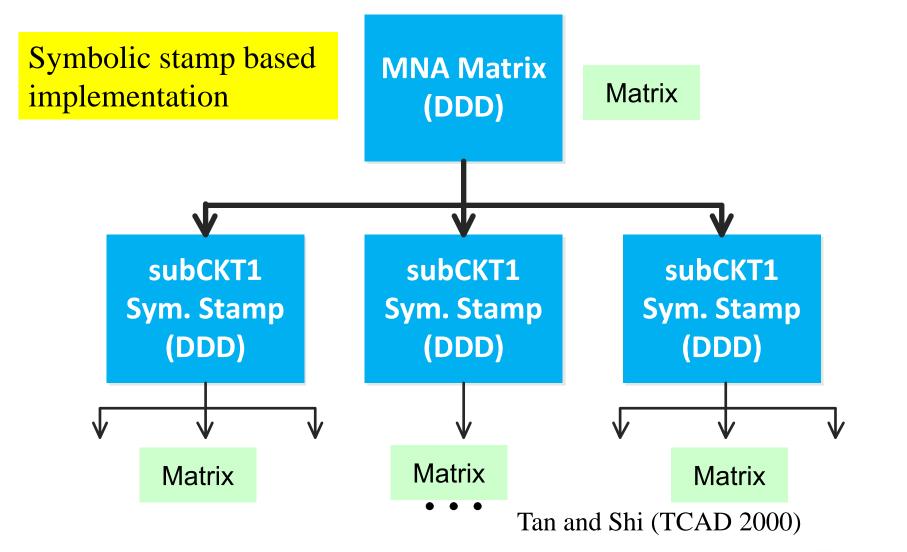

- Method 1. by hierarchical DDD (Tan-Shi TCAD 2000)

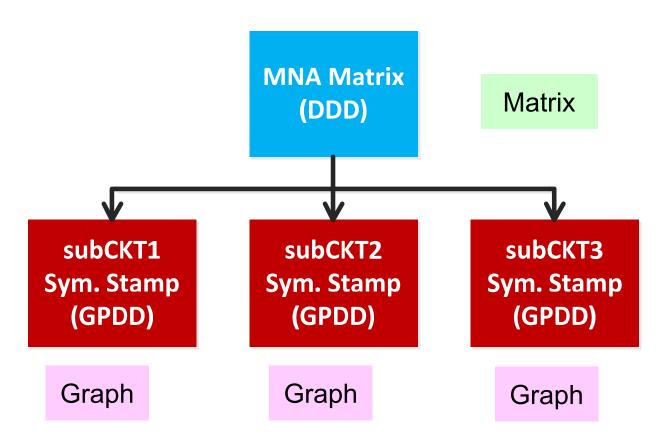

- Method 2: by GPDD + DDD (Xu et al. ASPDAC 2011)

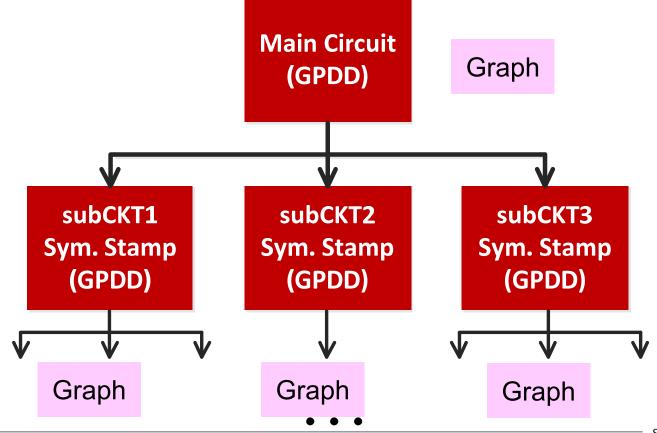

- Method 3) by hierarchical GPDD (this work)

We mainly compare **Methods 1 and 3** in this work.

#### Method 1: Hierarchical DDD

School of Micro-Electronics *EDA GROUP*

#### Method 2: GPDD+DDD

Limitation: only two-layers

Xu, Shi, and Li (ASPDAC 2011)

#### **Method 3: Hierarchical GPDD**

- Contribution of this work

- Purely graphical (based on circuit topology)

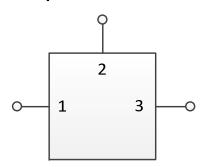

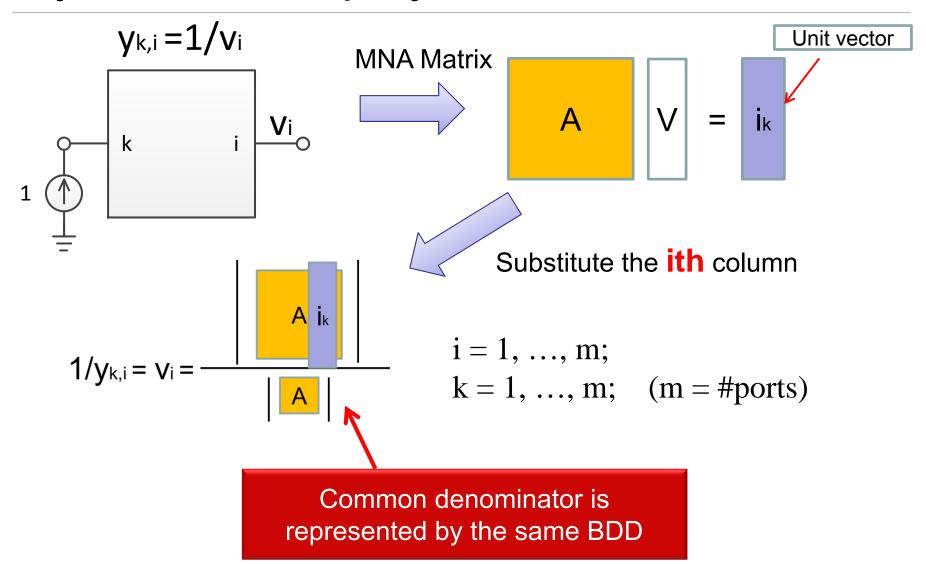

#### Key Technique

A graphical treatment of m x m stamp (m > 1).

$$\begin{pmatrix} i_1 \\ i_2 \\ i_3 \end{pmatrix} = \begin{pmatrix} y_{11} & y_{12} & y_{13} \\ y_{21} & y_{22} & y_{23} \\ y_{31} & y_{32} & y_{33} \end{pmatrix} \begin{pmatrix} v_1 \\ v_2 \\ v_3 \end{pmatrix}$$

3x3 VCCS

$$i_k = y_{k,m} v_m$$

A 3-port multi-dimensional VCCS is treated as nine regular (1x1) VCCS's, among them 3 are admittances.

Each regular VCCS can be treated by graph-pair reduction rules. (Shi et al, ASPDAC 2006)

#### **Experimental Results**

- Implemented in C++

- Machine:

- Intel Core2 Duo 1.80GHz processor

- 2GB memory

- Tested on <u>three</u> large operational amplifiers

- Unsolvable by flat symbolic analysis

- Compare two hierarchical methods

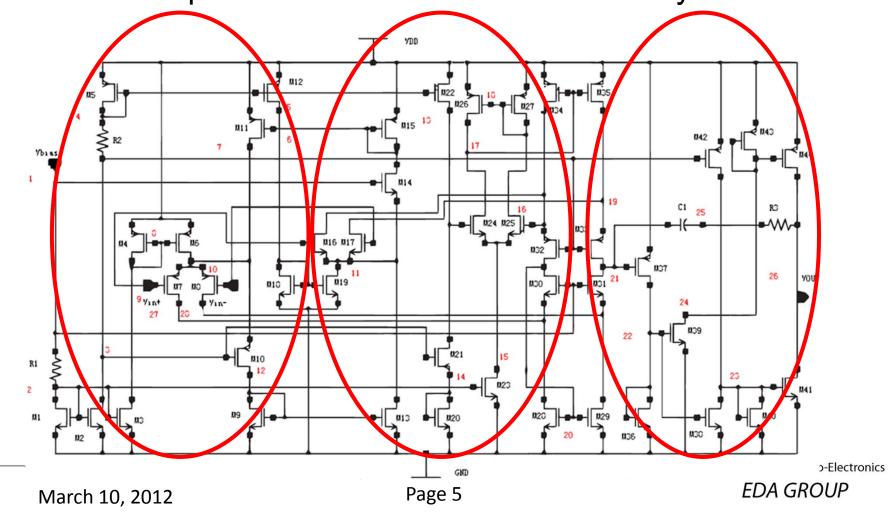

#### μA725 – Partition 1

Benchmark 1: µA725 opamp, containing 26 BJT transistors

#### Performance

**Circuit Partition**

| Module | GPDD    | GPDD<br>Constr.<br>Time (sec) |  |

|--------|---------|-------------------------------|--|

| L1,1   | 773     | 0.016                         |  |

| L2,1   | 548     | 0.046                         |  |

| L2,2   | 135,785 | 3.015                         |  |

| L2,3   | 91,682  | 2.067                         |  |

| Total  | 228,788 | 5.165                         |  |

#### μA725 – Partition 2

#### Performance

#### **Circuit Partition**

| Module | GPDD   | GPDD<br>Time(s) |  |

|--------|--------|-----------------|--|

| L1,1   | 773    | 0.016           |  |

| L2,1   | 548    | 0.046           |  |

| L2,2   | 2,987  | 0.099           |  |

| L2,3   | 700    | 0.066           |  |

| L3,1   | 99     | 0.038           |  |

| L3,2   | 103    | 0.043           |  |

| L3,3   | 476    | 0.045           |  |

| L3,4   | 126    | 0.038           |  |

| L3,5   | 133    | 0.05            |  |

| L3,6   | 131    | 0.05            |  |

| L3,7   | 4,822  | 0.13            |  |

| Total  | 10,898 | 0.67            |  |

School of Micro-Electronics

EDA GROUP

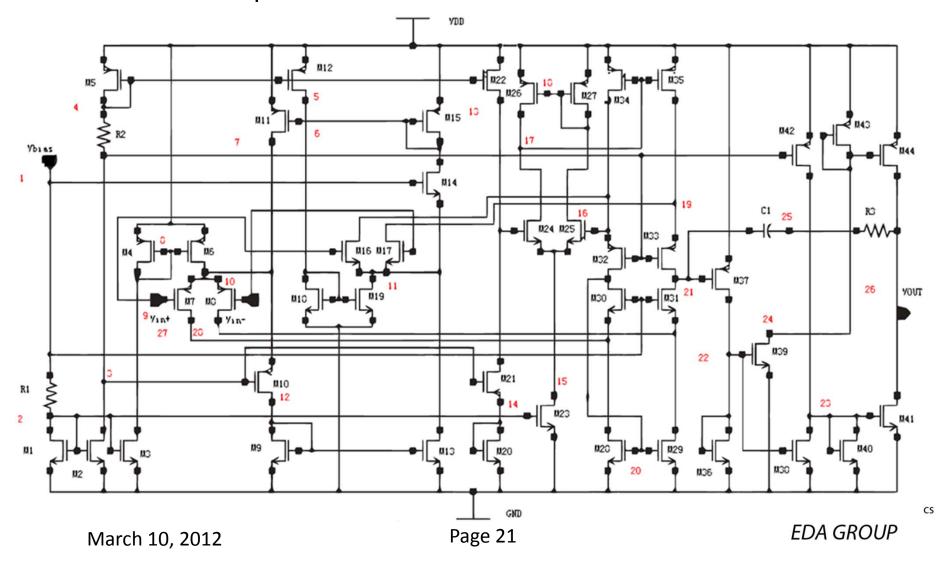

#### Benchmark 2

A MOSFET rail-to-rail cascode amplifier containing 24 MOS transistors VDD M19 16 Vin2 Vin1 GND School of Micro-Electronics

#### Benchmark 3

A MOSFET amplifier with 44 MOS transistors

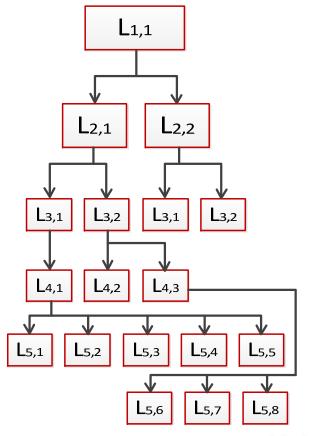

#### **Hierarchical Partitions**

#### **Benchmark 2**

# L<sub>1,1</sub> L<sub>2,1</sub> L<sub>2,2</sub> L<sub>2,3</sub> L<sub>2,4</sub> L<sub>3,1</sub> L<sub>3,2</sub> L<sub>3,3</sub> L<sub>3,6</sub> L<sub>3,4</sub> L<sub>3,5</sub>

#### **Benchmark 3**

#### Performance

Comparison of construction time between methods 1 and 3 (method 2 does not apply.)

|                |         | Met     | thod 3          | Method 1 |                |  |

|----------------|---------|---------|-----------------|----------|----------------|--|

| Circuit        | #Levels | GPDD    | GPDD<br>Time(s) | DDD      | DDD<br>Time(s) |  |

| Benchmark<br>2 | 3       | 17,488  | 0.793           | 11,506   | 2.042          |  |

| Benchmark<br>3 | 5       | 197,274 | 6.771           | 62,794   | 10.359         |  |

#### Comments

- Both hierarchical DDD and GPDD can solve large op-amp circuits.

- But the runtime performance of DDD or GPDD depends on the "symbol ordering" and the implementation details (e.g. hashing).

- Other differences remain to be explored in design applications.

#### Summary

Proposed a new hierarchical symbolic method by graph reduction

- Compared two hierarchical methods (DDD/algebraic and GPDD/graphical)

- Based on "symbolic stamp" implementations

### Thanks Q & A

School of Micro-Electronics EDA GROUP